VDHL教程 集成電路設計與太陽能發電系統的電子版應用

VHDL(VHSIC Hardware Description Language)是一種用于描述數字電路和系統的硬件描述語言,廣泛應用于集成電路設計領域。本教程將介紹VHDL的基礎知識、集成電路設計的應用,以及其在太陽能發電系統中的電子版實現。

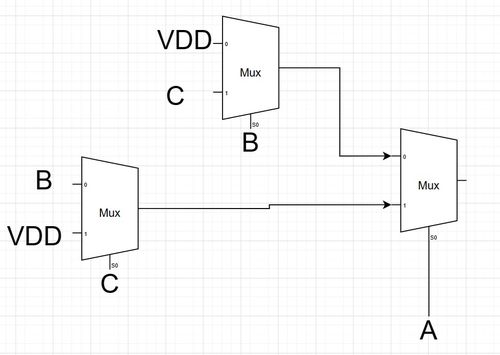

VHDL允許工程師通過代碼描述電路的行為和結構,從而在軟件環境中模擬和驗證設計。這大大縮短了集成電路的開發周期,減少了物理原型的成本。學習VHDL需要掌握數據類型、進程語句和組件實例化等核心概念。

在集成電路設計中,VHDL常用于實現復雜的邏輯功能,如微處理器、存儲控制器和通信接口。通過電子版工具(如ModelSim或Vivado),設計師可以編譯、仿真和綜合VHDL代碼,生成可編程邏輯器件(如FPGA)的配置文件。

VHDL在太陽能發電系統中也發揮著重要作用。例如,它可用于設計太陽能逆變器的控制電路,優化能量轉換效率。通過電子版教程,學習者可以訪問在線資源、模擬環境和代碼示例,快速上手實際項目。

掌握VHDL不僅有助于集成電路設計,還能推動可再生能源技術如太陽能發電的創新。推薦初學者從基礎語法入手,結合電子版教程進行實踐,逐步提升設計能力。

如若轉載,請注明出處:http://m.paopdyw.com/product/10.html

更新時間:2026-03-17 04:48:20