超大規模集成電路設計 基本概念(二)

超大規模集成電路(VLSI)設計是電子工程領域的重要組成部分,涉及在單一芯片上集成數百萬甚至數十億個晶體管。在前一篇文章中,我們介紹了VLSI的基本定義和歷史發展。本節將進一步探討集成電路設計的關鍵概念,包括設計流程、設計方法以及相關挑戰。

1. 集成電路設計流程

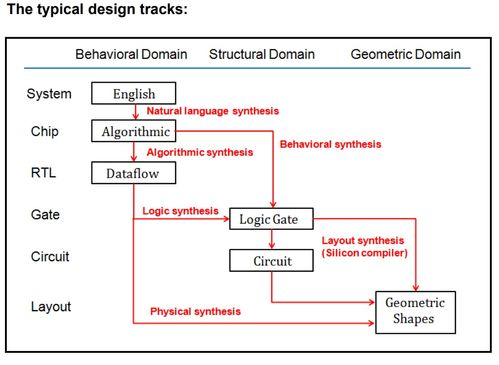

集成電路設計通常遵循一個標準化的流程,以確保高效和準確。該流程包括以下幾個主要階段:

- 規格定義:明確芯片的功能、性能要求和功耗限制。這是設計的基礎,涉及與客戶的溝通和技術分析。

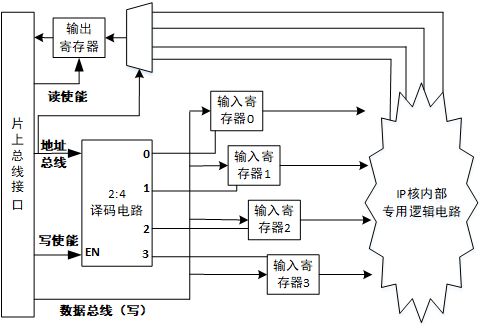

- 架構設計:確定芯片的整體結構,如處理器核心、內存模塊和接口。這包括選擇合適的設計方法,例如RTL(寄存器傳輸級)描述。

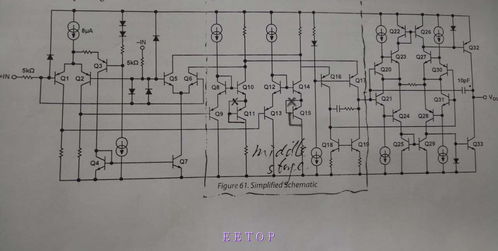

- 邏輯設計:使用硬件描述語言(如Verilog或VHDL)實現電路的邏輯功能。這一階段注重功能的正確性和優化。

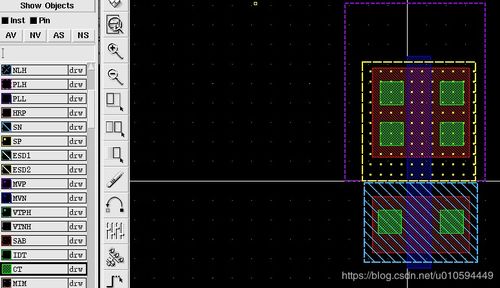

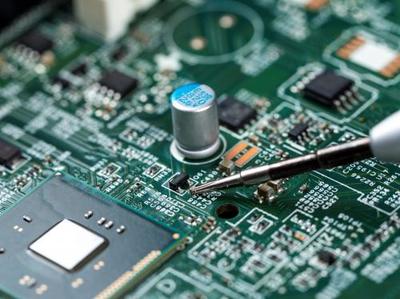

- 物理設計:將邏輯設計轉換為實際的物理布局,包括布局規劃和布線。這需要考慮制造工藝的限制,如最小線寬和間距。

- 驗證與測試:通過仿真和實際測試驗證設計的正確性,確保芯片在制造后能正常工作。

整個過程通常采用迭代方式,以解決設計中的錯誤和性能瓶頸。

2. 設計方法與工具

現代VLSI設計依賴于多種方法和工具,以提高效率和可靠性:

- 自頂向下設計:從高層次抽象開始,逐步細化到具體實現。這種方法便于團隊協作和錯誤管理。

- EDA工具:電子設計自動化(EDA)工具如Cadence和Synopsys,廣泛應用于設計、仿真和驗證。這些工具幫助設計師處理復雜的電路細節。

- IP核重用:為了縮短開發時間,設計師經常使用預設計的知識產權(IP)核,如處理器核心或內存控制器。這促進了模塊化設計。

3. 挑戰與未來趨勢

盡管VLSI技術不斷進步,但設計過程仍面臨諸多挑戰:

- 功耗管理:隨著芯片集成度的提高,功耗和散熱問題日益突出。低功耗設計技術如時鐘門控和電源門控成為關鍵。

- 制造復雜性:先進工藝節點(如7nm或以下)引入了新的物理效應,如量子隧穿,這要求設計工具和方法的持續創新。

- 成本與時間壓力:設計超大規模芯片需要巨額投資和長時間開發,因此優化設計流程以降低成本至關重要。

未來,VLSI設計將朝著更智能化、自動化方向發展,結合人工智能和機器學習技術,以應對日益復雜的需求。

超大規模集成電路設計是一個多學科交叉的領域,融合了電子學、計算機科學和材料科學。通過理解基本概念和流程,設計師能夠創造出高性能、低功耗的芯片,推動技術進步。在后續文章中,我們將深入探討具體設計技術和案例分析。

如若轉載,請注明出處:http://m.paopdyw.com/product/16.html

更新時間:2026-03-17 08:25:05