模擬CMOS集成電路仿真設(shè)計(jì)基礎(chǔ) 共漏跟隨器與軟件開(kāi)發(fā)

在模擬CMOS集成電路設(shè)計(jì)領(lǐng)域,共漏跟隨器(Common-Drain Amplifier,又稱源極跟隨器)是一種重要的基礎(chǔ)電路結(jié)構(gòu)。它以其低輸出阻抗、高輸入阻抗和單位電壓增益特性,廣泛應(yīng)用于緩沖級(jí)、電平移位和驅(qū)動(dòng)負(fù)載等場(chǎng)景。本文將從共漏跟隨器的基本原理出發(fā),結(jié)合軟件開(kāi)發(fā)流程,介紹仿真設(shè)計(jì)的基礎(chǔ)知識(shí)。

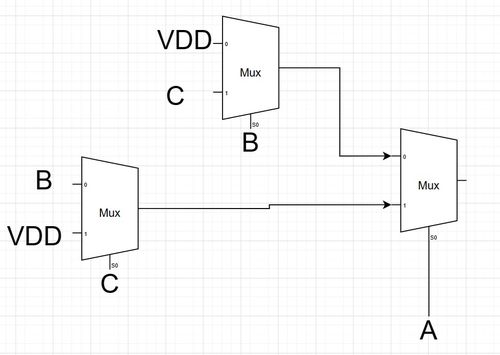

共漏跟隨器的核心是一個(gè)NMOS或PMOS晶體管,其柵極作為輸入端,源極作為輸出端,而漏極則連接到電源或地(取決于晶體管類型)。當(dāng)輸入信號(hào)施加到柵極時(shí),源極電壓會(huì)跟隨柵極電壓變化,但存在一個(gè)閾值電壓的偏移。這種結(jié)構(gòu)的主要優(yōu)點(diǎn)包括:輸入阻抗高,幾乎不從前級(jí)汲取電流;輸出阻抗低,能夠有效驅(qū)動(dòng)容性負(fù)載;以及電壓增益接近1,提供良好的信號(hào)隔離。共漏跟隨器也存在一定的局限性,例如輸出電壓擺幅受限和潛在的穩(wěn)定性問(wèn)題,需要在設(shè)計(jì)中仔細(xì)考慮。

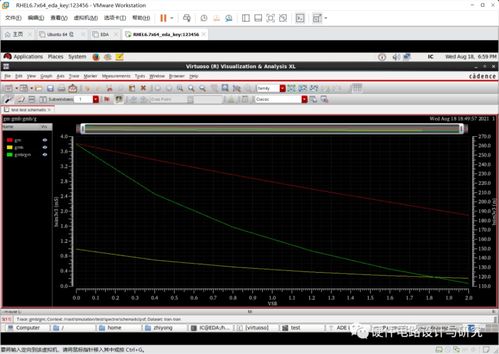

在仿真設(shè)計(jì)過(guò)程中,軟件開(kāi)發(fā)工具扮演著關(guān)鍵角色。常用的EDA(電子設(shè)計(jì)自動(dòng)化)軟件如Cadence Virtuoso、LTspice或HSPICE可以幫助工程師快速構(gòu)建電路模型、設(shè)置仿真參數(shù)并分析結(jié)果。設(shè)計(jì)流程通常包括以下幾個(gè)步驟:使用軟件繪制共漏跟隨器的電路圖,定義晶體管尺寸、偏置電壓和負(fù)載條件;進(jìn)行DC分析以確定工作點(diǎn),確保晶體管處于飽和區(qū);接著,執(zhí)行AC小信號(hào)分析,評(píng)估頻率響應(yīng)、輸入輸出阻抗和增益;通過(guò)瞬態(tài)分析驗(yàn)證電路在時(shí)域下的性能,如信號(hào)跟隨能力和失真情況。

軟件開(kāi)發(fā)不僅限于電路仿真,還包括參數(shù)優(yōu)化和蒙特卡洛分析,以應(yīng)對(duì)工藝變化。例如,在共漏跟隨器設(shè)計(jì)中,工程師可能需要調(diào)整晶體管的寬長(zhǎng)比(W/L)來(lái)平衡輸出阻抗和功耗,或者使用腳本自動(dòng)化仿真任務(wù),提高設(shè)計(jì)效率。集成版圖設(shè)計(jì)工具可以協(xié)助生成物理布局,確保電路在實(shí)際制造中的可靠性。

共漏跟隨器是模擬CMOS設(shè)計(jì)中的基礎(chǔ)模塊,通過(guò)結(jié)合先進(jìn)的軟件開(kāi)發(fā)方法,設(shè)計(jì)者能夠高效地進(jìn)行仿真和優(yōu)化,從而提升電路性能。掌握這些基礎(chǔ)技能,對(duì)于深入學(xué)習(xí)更復(fù)雜的集成電路系統(tǒng)至關(guān)重要。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.paopdyw.com/product/9.html

更新時(shí)間:2026-03-17 14:55:24